# **KHWARIZMIA**

Vol. (2023), 2023, pp. 103–112 ISSN: 3078-2694

# **Research Article**

# Efficient Hardware Acceleration Techniques for Deep Learning on Edge Devices: A Comprehensive Performance Analysis

M.A. Burhanuddin<sup>1,\*</sup>,

<sup>1</sup> Faculty of Information & Communication Technology, University Teknikal Malaysia Melaka, Durian Tunggal, Melaka, Malaysia

#### **ARTICLE INFO**

Article History Received 1 May 2023 Revised: 15 Jun 2023 Accepted 15 Jul 2023 Published 1 Aug 2023

Keywords Edge Devices Hardware Acceleration Deep Learning GPUs Energy Efficiency

#### ABSTRACT

Implementing deep learning models on edge devices presents significant challenges due to the limited computing power, memory limitations, and processing power of these devices As deep learning models become more complex, cf ensuring proper execution on an edge platform is critical for real-time implementation Hardware -Addresses these challenges by exploring ways to accelerate. The problem lies in the resource-hungry nature of today's deep learning models, which are typically designed for cloud environments with high computing capacity, making them unsuitable for edge environments with restricted resources. The main objective of this review is to analyze and compare various hardware acceleration strategies, such as graphics processing units (GPUs), tensor processing units (TPUs), field programmable gate arrays (FPGAs), and application-specific integrated circuits (ASICs); (pruning, quantization, and knowledge storage), memory management, and data flow optimization to improve the performance and energy efficiency of deep learning models on edge devices the results of this comprehensive performance analysis suggests that hardware accelerators can significantly improve throughput and reduce latency while maintaining acceptable levels of power consumption and accuracy. In addition to techniques such as quantization and pruning that are seen to reduce computational load and memory footprint, enabling more efficient deep learning inference on edge platforms, the study highlights trade-offs between speed, consumption power efficiency and model accuracy between for each hardware accelerator are emphasized. The findings suggest that by choosing the right hardware and applying the right optimization techniques, edge devices may be able to optimize deep learning models, meeting the requirements of real-time AI applications in resource-constrained environments handle the role there.

# 1. INTRODUCTION

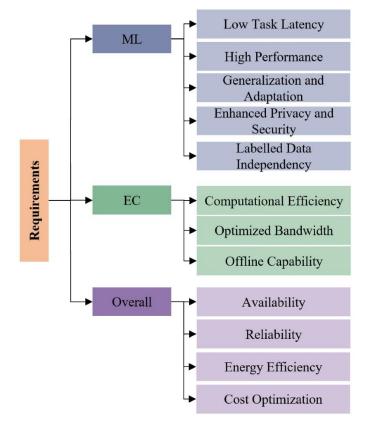

Deep learning has emerged as a revolutionary technology in a variety of industries, from artificial intelligence (AI) to the Internet of Things (IoT). It powers a wide range of modern applications, including autonomous vehicles, medical research, smart devices, and natural language processing. Deep learning models have been widely adopted because of their ability to learn from large amounts of data and make decisions in real time. But many of these applications require simple operations and real-time decision-making, which pose significant challenges, especially in edge computing environments where machines work with compressed objects Very deep learning notwithstanding computing power, memory and energy availability limitations in the case of IoT are the edge devices that must be developed[1]. Traditional deep learning models, typically developed and trained in cloud environments with large amounts of computing resources, are ineffective when run on edge devices High computational costs, with resource constraints including, make it difficult to obtain real-time statistics, an important requirement for many IoT applications Dissonance: Energy -Requires the use of special hardware acceleration techniques to ensure performance is not compromised while maintaining operational efficiency[2]. This paper aims to explore various hardware acceleration techniques to meet the challenge of applying deep learning models to edge devices that can improve computing performance without sacrificing performance In particular, high hardware acceleration, the as GPUs, TPUs, FPGAs, and ASICs, to enable deep learning to optimize model execution in resource-constrained edge situations. Applications will be explored These accelerators are designed, through their design and capabilities, to increase the efficiency of AI operations by providing parallel processing power and reducing the computational cost of deep learning models [3]. The main objectives of this paper are twofold: first, to examine the use of hardware accelerators for deep learning in wearable devices and to analyze their relative strengths and weaknesses. Second, by conducting a comprehensive performance analysis comparing key metrics such as latency, power consumption, throughput, and computational accuracy across different hardware platforms, this paper aims to provide insights a valuable relative to that of various edge device applications Hardware acceleration techniques are most suitable The scope of this paper includes a review of hardware and software techniques that enable very deep learning on edge devices. It will explore key features of edge devices, such as their computation and power limits, and how these features affect the development and implementation of deep learning models. The paper will cover a range of hardware accelerators, including basic general tools, and provide detailed performance comparisons based on real-world simulations and case studies [4]. In order to to guide the reader through these topics, the paper is organized as follows: They are limited to reviewing the challenges posed for deep learning implementations in general and discussing various hardware acceleration strategies, including GPUs, including TPUs, FPGAs, and ASICs, highlighting their respective advantages and trade-offs followed by optimization of compression and energy efficiency design f and exploring new optimization methods. The paper will then present a detailed performance analysis of these techniques, showing the impact of hardware acceleration on deep learning models using real-world data Finally, the paper will conclude by discussing current challenges and possible future directions in this rapidly growing field. This program will provide a comprehensive understanding of the most efficient hardware acceleration techniques for deep learning on edge devices and provide valuable guidance to researchers and industry professionals seeking to optimize AI performance in environments with limited resources [5]. Figure 1 illustrates the requirements for an effective machine learning (ML) and edge computing (EC) algorithm, as well as an overall optimization algorithm. For ML, several important features have been emphasized, such as low workload, which makes the real-time or near-real-time model operational, and high performance, which occurs emphasizing the need for effective auditing. Enhanced privacy and security are especially important in ML applications to protect sensitive data, especially when dealing with edge devices. Furthermore, labeled data independence focuses on the ability of ML algorithms to operate efficiently on limited amounts of labeled data, which is important in many practical situations where labeled data are scarce with a focus on performance and increasing autonomy for EC. Technical excellence ensures that edge devices can handle complex tasks with minimal computing power, while optimized bandwidth reduces the need for continuous transfer of data to the cloud, and reduces communication costs and latency Important in limited environments[6].

Fig 1. Key Requirements for Efficient Machine Learning and Edge Computing Systems

# 2. OVERVIEW OF EDGE DEVICES AND HARDWARE CONSTRAINTS

Edge devices, including smartphones, IoT sensors, wearable technology and embedded systems, play a key role in modern computing by processing data at the source rather than relying on remote data centers or cloud infrastructure but those devices this is inherently redundant Three major limitations are memory, processing capacity and energy consumption. First, edge devices generally have limited memory capacity compared to high-performance computing, such as cloud data centers. Many deep learning models require large amounts of memory to store weights, processors, and intermediate results during inference. However, edge devices typically use a fraction of the memory of traditional servers, forcing manufacturers to use

smaller custom models or use techniques such as memory swapping, which can affect performance in a way negatively over Second, edge devices power consumption is another important limitation [7]. While some edge devices come with special chips optimized for low-power performance (such as ARM processors), their computing power is much lower than the general-purpose processors or GPUs found in cloud servers. This makes it difficult for edge devices to handle complex deep learning models with millions of parameters with many layers, resulting in higher computation time and reduced throughput Finally, energy consumption implementation is crucial for edge devices, especially those Battery-powered devices, such as drones, mobile phones, or IoT sensors in remote locations must be balanced on materials efficiency and energy efficiency to ensure the longevity and reliability of these devices. Running deep learning models at full capacity can rapidly drain battery life, making low-power performance a key concern for implementing AI in in the river [8].

#### 2.1 Comparison with Cloud Computing in Terms of Latency and Scalability

Deep learning models in cloud computing environments benefit from powerful hardware resources, including highperformance CPUs, GPUs, and highly distributed computing systems This enables training and execution of deep learning love a complex model on a scale not possible on edge devices. But deploying AI models in the cloud also comes with its own set of challenges, especially in terms of latency and scalability. The latency or time delay in transferring data between an edge device and the cloud is one of the main reasons AI computing is pushed closer to the edge. For real-time applications such as autonomous driving or real-time video analysis, even slightly delayed decisions can have serious consequences. In cloud-based systems, data must travel to and from the data center, which causes latency due to network transmission times, especially in remote locations or bandwidth-constrained Edge computing mitigates this by providing data as it controls the operations locally, significantly reducing latency and enabling real-time operational decision making [9]. Scalability is another aspect of cloud computing that has its advantages, as it allows organizations to distribute dynamic resources based on demand. But relying solely on the cloud is not practical for applications that require immediate response or continuous operation in environments with unreliable connectivity Edge Computing, which has its design a decentralized, provides a highly scalable solution by distributing computing tasks between local devices, and allows for greater complexity and AIdriven responsiveness of applications.

#### 2.2 Challenges in Deep Learning on Edge

Implementing deep learning models on edge tools presents some unique challenges, mainly due to how computationallyresource-intensive these models are Required. While cloud environments can support the training of these models, running simulations on edge devices can be problematic due to their limited processing capabilities One of the biggest challenges in learning a depth at the edges and the need for real-time reflections [10]. Decisions must be made immediately on applications such as autonomous systems, monitoring, or real-time health monitoring. However, the complexity of today's deep learning models tends to introduce high latency when evaluating resource-intensive devices, which can lead to delayed responses or degraded user experience s-Consumption is a significant bottleneck Since many holding devices operate in environments where available energy is limited, it is necessary to operate them with low energy consumption. But deep learning systems are notoriously power hungry, requiring large amounts of computing resources for even the simplest tasks. As a result, running these graphics on edge devices that have no optimization options can slow down battery life or overheat the device, making it useless are not controlled to continue to be used in real-world applications and therefore powered by deep learning techniques, hardware -Adaptation is likewise necessary to sustain AI in edge environments. In summary, although edge devices offer the benefits of reduced latency and scalability for real-time applications, their inherent limitations in terms of memory, processing power, and energy consumption pose challenges great comes deep learning deployment Paradigms optimized to address these challenges, efficient Special hardware accelerators are designed to improve algorithm development, performance and energy efficiency balance is important This balance is necessary for AI to be effective in applications more depending on the edges [11].

#### 3. HARDWARE ACCELERATORS FOR DEEP LEARNING ON EDGE DEVICES

Hardware accelerators are specialized computing devices designed to improve specific performance by moving heavy computing power away from general-purpose CPUs In the AI industry, hardware accelerators are essential for computation the deep functionality required by deep learning models, such as matrix multiplication, confusion and processing are highly scalable, making them ideal candidates for hardware acceleration. The main role of hardware accelerators in deep learning is to accelerate the inference process by performing these computations more efficiently than general-purpose processors, and by reducing power consumption. This is especially important in wearable devices, which have limited computing resources and power, and often require real-time processing. By using hardware accelerators, edge devices can meet the complexity of today's deep learning model with improved performance efficiency. Running those models on a CPU alone without accelerators would not only slow down inference times but also waste the limited resources of edge machines so hardware accelerators provide the computational boost necessary for deep learning efficient inferences while maintaining a low level of processing power play an important role in enabling edge-AI [12].

#### **3.1 Types of Hardware Accelerators**

There are several hardware accelerators designed to enable deep learning tasks on wearable devices. These include graphics processing units (GPUs), tensor processing units (TPUs), field programmable gate arrays (FPGAs), and application-specific integrated circuits (ASICs), each offering unique advantages and trade-offs depending on the specific application.

GPUs (Graphics Processing Units): GPUs are the most widely used hardware accelerators for deep learning because of their ability to perform highly parallel calculations, which is a starting point for deep learning models. Their high resolution allows them to handle multiple applications simultaneously, making them ideal for fast training and simulation of deep learning models but GPUs consume more power than other accelerators, which can be a drawback at edge environments where energy efficiency is important. Despite this, their versatility and availability make them a popular choice for edge AI, especially in applications that require a balance between performance and flexibility [13].

TPUs (Tensor Processing Units): TPUs are special accelerators developed by Google specifically for deep learning work. Unlike general processor acceleration GPUs, TPUs are optimized for a variety of tasks commonly used in machine learning models, such as tensor functions TPU types can provide higher performance than GPUs in some deep learning tasks, especially those involving matrix multiplication and convolution, . One of the main advantages of the TPUs that tend to go over neural networks is their energy efficiency, as they are designed to deliver higher performance while consuming less power compared to a GPU. This makes TPUs an attractive option for edge devices where power constraints are an important consideration. But TPUs are not as flexible as GPUs, because they are designed primarily for deep learning and may not be suitable for general-purpose computing [14].

FPGAs (Field Programmable Gate Arrays): FPGAs are reconfigurable hardware accelerators that can be programmed to perform specific tasks with efficiency. Unlike fixed-function accelerators like GPUs and TPUs, FPGAs can be tailored to the specific requirements of a particular deep learning model, allowing you to optimize for a specific application This flexibility enables FPGAs balancing performance and power management capabilities, making them a valuable choice for edge devices that may require different applications or application models FPGAs are known for their energy efficiency and potential for increased performance great improvement for deep learning theory when configured properly. But programming FPGAs is more complex compared to GPUs and TPUs, so it requires specialized knowledge in Hardware Description Language (HDLs) and low-level programming This can make development slow and difficult, but the benefits of custom optimization are often than the stronger edge functions.

ASICs (Application-Specific Integrated Circuits): ASICs are custom chips designed for a specific application, in this case deep learning. Unlike GPUs, TPUs, and FPGAs, which are general or reconfigured accelerators, ASICs are built from the ground up to perform specific tasks efficiently because they are so unique, ASICs can offering better performance and energy efficiency than others accelerators. This makes them a good choice for edge devices that require routine and low-power deep learning models, such as smartphones, autonomous vehicles, or wearable devices but the main drawback of ASICs is their lack of flexibility; They are designed to perform specific tasks and cannot be easily reused for other uses. Furthermore, ASICs have high development costs, as they require customized hardware design and manufacturing, making them a less robust option for many applications compared to *simpler accelerators such as GPUs and FPGAs [15]*.

#### **3.2 Comparison of Accelerators**

Each hardware accelerator offers unique benefits and trade-offs in terms of power efficiency, latency and performance, making it important to choose the right accelerator based on the specific needs of the edge application

GPUs, with their high levels of parallelism, excel in delivering performance for a wide range of deep learning models, but their processing power is relatively high, making edge devices not ideal for power-sensitive applications. They are also common introduces some latency from their general purpose nature.

TPUs provide excellent stability and are specially designed for deep learning performance, making them very efficient for matrix multiplication etc. Their main strength is to reduce latency and power consumption compared to GPUs, but their unique characteristics limit their flexibility for other tasks.

FPGAs offer a unique balance of power efficiency and switching, as they can be tailored to provide optimal performance and power consumption for specific applications. This makes them ideally suited for edge environments where deep learning tasks may be required. But their programming complexity and low-level optimization requirements can be a hindrance.

ASICs offer high levels of performance and energy efficiency for a given application but at the cost of high modification and upgrade costs. They are ideal for applications that require dedicated rapid deep learning in low-power environments, but are not suitable for environments that require multimodal or multiple applications

Table I summarizes the common methods for optimizing deep learning performance on edge devices with critical features. Each approach addresses specific challenges related to memory, power management, and energy efficiency. For example, appropriate compression techniques such as pruning, quantification, and knowledge distillation aim to reduce model complexity as it continues to execute, even if it results in a trade-off in accuracy [16]. Technology and memory optimization focus on improving data stream performance and resource utilization, while hardware design in particular targets techniques such as low-energy architecture, approximate computation, and so on energy efficiency software programs such as TensorFlow Lite and ONNX Runtime enable models to be efficiently run on different hardware platforms, but for specific

hardware. Optimizations may have their limitations Finally, model splitting allows joint inference between edge devices and the cloud, balancing computational load but requiring a reliable network connection This consideration reveals how each method has different limitations and well suited for various application areas for autonomous systems and industrial automation for IoT adi and mobile devices.

| Method                                                  | Description                                                                     | Limitations                                                                         | Application Areas                                                    |

|---------------------------------------------------------|---------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|----------------------------------------------------------------------|

| Model Compression                                       |                                                                                 |                                                                                     |                                                                      |

| Techniques                                              |                                                                                 |                                                                                     |                                                                      |

| - Pruning                                               | Removing redundant parameters to reduce model size                              | May lead to a slight loss in model accuracy                                         | Image classification, object detection, NLP                          |

| - Quantization                                          | Reducing the precision of weights<br>and activations (e.g., 32-bit to 8-bit)    | Can result in a drop in accuracy, especially for highly complex models              | Real-time video processing,<br>speech recognition, mobile<br>devices |

| - Knowledge Distillation                                | Training a smaller model (student)<br>to mimic a larger model (teacher)         | Requires additional training and may<br>not fully capture complex model<br>behavior | Autonomous driving, edge AI for IoT, wearable devices                |

| Optimization of<br>Computation and Memory               |                                                                                 |                                                                                     |                                                                      |

| - Operator Fusion                                       | Merging multiple layers or<br>operations to reduce memory access<br>overhead    | Limited to specific layers and<br>operations, complexity in<br>implementation       | AI inference on mobile devices, real-time analytics on edge          |

| - Efficient Memory<br>Management                        | Optimizing memory usage to<br>minimize off-chip memory access                   | May not be as effective with very large models; complex to implement                | IoT sensors, embedded AI applications                                |

| - Parallelism and Dataflow<br>Optimization              | Utilizing parallel processing and<br>optimizing data flow between<br>components | Not all models or algorithms can be efficiently parallelized                        | Robotics, drones, industrial automation                              |

| Specialized Hardware<br>Design for Energy<br>Efficiency |                                                                                 |                                                                                     |                                                                      |

| - Low-Power Hardware<br>Architectures                   | Custom hardware designs optimized<br>for AI tasks                               | High cost of design and manufacturing, limited flexibility                          | Autonomous systems,<br>wearables, smart cameras                      |

| - Clock and Power Gating                                | Selectively turning off inactive chip components to save power                  | Can introduce latency when reactivating components                                  | Battery-powered edge devices<br>(e.g., health monitors, drones)      |

| - Approximate Computing                                 | Sacrificing precision for reduced<br>power consumption and speed                | Potentially significant accuracy loss in<br>sensitive applications                  | Perception tasks like image<br>recognition, smart assistants         |

| Edge AI Frameworks and<br>Software Optimizations        |                                                                                 |                                                                                     |                                                                      |

| - TensorFlow Lite                                       | Lightweight deep learning<br>framework for edge devices                         | Limited support for some hardware accelerators                                      | Mobile applications, IoT devices, smart home devices                 |

| - ONNX Runtime                                          | Optimizes models for cross-platform deployment on various accelerators          | May not fully exploit all hardware-<br>specific features                            | AI model deployment across<br>diverse edge hardware platforms        |

| - NVIDIA TensorRT                                       | Deep learning inference library for NVIDIA GPUs                                 | Limited to NVIDIA hardware, not portable across other platforms                     | High-performance AI tasks on NVIDIA-powered edge devices             |

| Model Partitioning and<br>Collaborative Inference       | Splitting deep learning models<br>between edge and cloud                        | Requires reliable connectivity to the<br>cloud, potential latency issues            | Edge-cloud hybrid applications, smart cities, industrial IoT         |

TABLE I. OVERVIEW OF CURRENT METHODS FOR EFFICIENT HARDWARE ACCELERATION OF DEEP LEARNING ON EDGE DEVICES

#### 4. TECHNIQUES FOR EFFICIENT HARDWARE ACCELERATION

Efficient hardware speed for deep learning on edge devices requires a combination of different model and hardware optimization techniques The goal is to balance computational performance with limited resources, such as memory, processing power, . and energy consumption, without significantly compromising the accuracy or efficiency of the models Key strategies for achieving balance include focusing on model compression, optimization techniques, and energy-efficient design strategies Providing the right approach hardware capabilities increase for deep learning on edge devices and model compression techniques. These techniques reduce the size and complexity of deep learning models, making them easier to run on resource-constrained hardware. The three main best practices for compression are pruning, quantization and knowledge distillation [17]. Pruning removes redundant or redundant parameters from the neural network, effectively simplifying the model. During the training phase, many models over-parameterize, resulting in unnecessary combinations or weights. The systematic removal of these reduces the computational burden during calculation. For example, structured cuts eliminate all filters or veins, significantly reducing image size while maintaining precision. However, if not used carefully, pruning can slightly reduce accuracy, but provides significant improvements in computational efficiency and memory consumption in edge devices Quantization reduces load and activation accuracy from 32-bit floating-point values to low-precision formats such as -bit numbers that are integer [18]. This greatly reduces memory and computation requirements, resulting in faster calculations and lower power consumption. Although lower accuracy may lead to a slight loss of accuracy, dose training may mitigate these effects. Quantization is particularly useful in applications such as mobile AI or IoT devices where both speed of processing and energy efficiency are important. Knowledge embedding is another form of inspiration that allows a small "learner" sample to learn from a larger, more complex "learner" sample. The simpler and more efficient student model mimics the behavior of the teacher model but with fewer parameters and fewer computational requirements. This approach ensures that the student model retains the instructor's core skills while being more suitable for use with wearable devices. The trade-off is that the student model doesn't adequately reflect the instructor's challenges, but it works well for real-time tasks such as image recognition or voice processing. In addition to the compression model, optimizing how computation is done in hardware is essential to optimize performance. This is achieved through a variety of software and hardware-level optimizations, including memory management, storage and communication minimization, and data flow and parallelism enhancement Memory management and storage play a key role in ensuring edge devices run slow, on a chip. You can manipulate data without much external memory. Techniques such as memory tiling, in which large data inputs are divided into smaller tiles that can fit on-chip memory, allow for faster performance by eliminating the need for regular memory replacement Additionally, be sure that more efficient caching methods do so in order to store frequently accessed data locally, further reducing the delay associated with memory accesses [19]. These techniques are particularly useful for inputting large amounts of data, such as images or video, which is common in deep learning applications on edge devices Reducing connectivity is another key optimization factor. Many deep learning models need to move data between different components, such as CPU, memory, and special accelerators (e.g. GPUs or TPUs) Reducing communication channels reduces latency and power consumption by multiplying and size reduced by this data transfer. This is especially important in edge areas where bandwidth is limited and energy resources are scarce. For example, consolidating multiple data inputs before processing can reduce the costs associated with data migration. Data flow improves how data is processed in hardware to increase parallelism and optimization. Data flow optimization refers to efficient ways to transfer data between processing units and memory, ensuring that bottlenecks are avoided. On the other hand, parallelism optimization makes better use of hardware accelerators by exploiting the inherent parallelism of deep learning models. For example, parallel tasks can distribute levels or tasks of neural networks across multiple processing units, while data parallelism can distribute input data across multiple cores to be processed simultaneously The two methods are all needed to harness the power of hardware accelerators such as GPUs, TPUs, and FPGAs, . significantly improving throughput and reducing latency in edge applications These optimization techniques ensure that edge devices make the best use of available hardware, reduce unnecessary delays or bottlenecks, and perform deep learning even if there are few computer resources. comply with policies [20].

#### 4.1 Energy-Efficient Design Techniques

For edge devices, especially those that rely on battery power or operate in energy-constrained environments, the primary concern is to minimize energy consumption Energy efficient design techniques aim to perform optimally for real-time deep learning inference. Power consumption should be reduced while maintaining high rates. Energy consumption analysis is the first step in designing energy efficient systems. By analyzing the parts of the system that use the most energy during the modeling process, the designer can focus on improving these areas. For example, shape multiplication and convolution operations are often the most power-consuming operations in deep learning models. Special hardware accelerators such as TPU and ASICs are designed to handle these applications more efficiently, reducing overall power consumption [21]. Power management strategies are needed to extend the battery life of edge devices without sacrificing performance. Techniques such as dynamic voltage and frequency measurement (DVFS) dynamically change the operating frequency and voltage of the hardware based on the current workload and when the workload is light, the system operates at a lower frequency and voltage, and conserves energy. Conversely, if a large computing load is detected, the system scales to meet the required performance. Another technique, called clock gating, turns off clock signals on idle pieces of hardware to reduce power consumption. On the other hand, power gating turns off unused resources altogether, saving energy when they are used [22]. These power management techniques are especially valuable in edge applications such as drones, wearables, IoT sensors, where preserving battery life is important to ensure long-term performance Table II provides a detailed comparison of different optimization techniques used to improve deep learning in edge devices And from model compression techniques such as quantization, which reduce model size and computational complexity, to memory management techniques such as tiling and caching, which increase memory efficiency improve and reduce latency. In addition, reduced communication and parallelism strategies optimize data flow and work distribution across hardware units, resulting in increased throughput, lower uptime and Finally, energy-depleted design methods, including DVFS, clock-gating, power- ing. Gating is also available, which helps reduce power consumption, make edge devices more durable and more energy efficient Each method offers trade-offs in performance, power consumption well and in electronics [23].

| TABLE IL COMPARISON OF OPTIMIZATION TECHN        | IQUES FOR EFFICIENT HARDWARE ACCELERATION     |

|--------------------------------------------------|-----------------------------------------------|

| THEELE II. COMITINGSON OF OF THIME THOSE TECHNIC | IQUED I OR ELLICIENT IN IRD WIRE NOULEER THON |

| Optimization Technique | Key Parameters                  | Measured Values                | Description                                                                            |

|------------------------|---------------------------------|--------------------------------|----------------------------------------------------------------------------------------|

| Model Compression      |                                 |                                |                                                                                        |

| Techniques             |                                 |                                |                                                                                        |

| - Pruning              | Percentage of parameters pruned | Typical pruning rates: 30%–90% | Reduces model size by removing redundant parameters. Trade-off between performance and |

|                        |                                 |                                | accuracy.                                                                              |

| - Quantization                                       | Precision (bit-width)                                        | 8-bit integer precision (INT8) vs.<br>32-bit floating point (FP32)                        | Reduces precision of weights and activations for<br>lower memory and faster inference, may slightly<br>impact accuracy.               |

|------------------------------------------------------|--------------------------------------------------------------|-------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|

| - Knowledge Distillation                             | Compression ratio (teacher-<br>to-student model size)        | Compression ratios: 2x to 10x                                                             | Trains a smaller student model to mimic a larger<br>teacher model. Can reduce model size<br>significantly with minimal accuracy loss. |

| Memory Management<br>and Caching                     |                                                              |                                                                                           |                                                                                                                                       |

| - Memory Tiling                                      | Tile size (input data chunks fitting in memory)              | Tile size depends on memory<br>capacity; typically, in kilobytes or<br>megabytes (KB, MB) | Breaks data into smaller tiles that fit within the<br>on-chip memory to reduce off-chip memory<br>access.                             |

| - Caching                                            | Cache hit ratio, cache size                                  | Cache hit ratio: 80%–95%                                                                  | Stores frequently accessed data locally in faster<br>memory to minimize latency and memory access<br>costs.                           |

| - Communication<br>Minimization                      |                                                              |                                                                                           |                                                                                                                                       |

| - Batching                                           | Batch size (number of<br>inputs processed<br>simultaneously) | Typical batch sizes: 8, 16, 32                                                            | Processes multiple inputs together to minimize<br>the frequency of data movement and optimize<br>throughput.                          |

| Dataflow and Parallelism                             | 27                                                           |                                                                                           |                                                                                                                                       |

| - Task Parallelism                                   | Number of tasks executed in parallel                         | Parallel execution rates: typically<br>2x to 4x speedup                                   | Distributes different parts of the model across multiple processing units to increase throughput.                                     |

| - Data Parallelism                                   | Input data split across<br>processing cores                  | Speedup factor: 2x to 8x                                                                  | Splits input data for simultaneous processing on multiple cores, useful for large-scale AI tasks.                                     |

| Energy-Efficient Design                              |                                                              |                                                                                           |                                                                                                                                       |

| - Dynamic Voltage and<br>Frequency Scaling<br>(DVFS) | Frequency, voltage                                           | Voltage: 0.8V–1.2V; Frequency: 500 MHz to 1.5 GHz                                         | Dynamically adjusts the voltage and clock<br>frequency to conserve energy during light<br>workloads.                                  |

| - Clock Gating                                       | Percentage of inactive circuits turned off                   | Power savings: up to 40%                                                                  | Turns off the clock signal to inactive hardware<br>components to reduce dynamic power<br>consumption.                                 |

| - Power Gating                                       | Power-off threshold (idle time before shutdown)              | Power savings: up to 60%                                                                  | Completely powers down idle hardware components, saving energy when components are not in use.                                        |

# 5. PERFORMANCE ANALYSIS OF ACCELERATION TECHNIQUES

The performance of hardware acceleration techniques for deep learning on edge devices is typically evaluated using four key metrics: throughput, latency, power consumption, and model accuracy Throughput refers to the number of concepts or applications handled by the hardware accelerator every second of the year. High throughput means more tasks are completed in a given time, which is important for real-time applications such as video processing or object recognition on edge devices Throughput is measured as processes per second or inferences per second (IPS). Latency is the time it takes for the system to process a calculation from input to output, usually measured in milliseconds (MS) [24]. For applications that require immediate responsiveness such as autonomous driving, healthcare monitoring, or robotics it's critical. Power consumption is an important consideration for edge devices, which typically have limited power consumption or run on batteries. It measures the amount of energy consumed by the hardware during the calculation, usually watts (W) or joules (J). Reducing power consumption while maintaining performance is a major challenge in edge computing environments. The accuracy of the model evaluates how well the deep learning model performs in terms of prediction quality. Metrics such as precision, recall, and F1-score are often used to evaluate the efficiency of a model. While improving throughput, latency, and power efficiency, it is important that the accuracy of the model does not deteriorate significantly. Together, these metrics provide a comprehensive view of the effort and benefits of using different hardware accelerators for deep learning on edge devices, contributing to speed, energy consumption and inference quality balanced [25].

# 5.1 Experimental Setup

Well-defined testing protocols are needed to evaluate the effectiveness of hardware acceleration methods. These programs typically involve selected edge devices, deep learning models, benchmarking tools and data sets. The fixtures used in the tests may vary depending on the complexity of the task and the environment. Common edge devices include smartphones, Raspberry Pi, Nvidia Jetson Nano, ARM-based devices and microcontrollers. These devices represent a wide range of hardware available for edge AI, each with different processing capabilities and power constraints. Deep learning models tested on these tools typically have lightweight architectures that are optimized for edge environments. Typical models include MobileNet for image segmentation, YOLO for object detection, and transformer-based models (such as BERT) for natural language processing (NLP). These models were chosen because they are widely used in real-world applications and represent a good balance between complexity and performance. Benchmarking tools such as TensorFlow Lite Benchmark Tool, MLPerf, and PyTorch Mobile are used to evaluate model performance on various hardware platforms. These tools provide comprehensive overviews of computation time, power consumption, and other key performance indicators, and

ensure that results are consistent and comparable across machines Sample testing datasets the view typically includes ImageNet for image classification, COCO for object recognition, and SQuAD for NLP The theory and These data sets provide a standardized way to view and compare the accuracy and performance of deep learning models in hardware accelerators.

#### 5.2 Performance Comparison

The performance of different hardware accelerators is compared based on the aforementioned evaluation metrics: throughput, latency, power consumption, and model accuracy Commonly tested hardware accelerators include GPUs, TPUs, FPGAs, and ASICs. GPUs (Graphics Processing Units) are widely used for deep learning due to their high parallel processing capabilities. They offer high throughput and low latency for real-time processing but consume a lot of power, which can be a drawback in edge environments with low power consumption TPUs (Tensor Processing Units) are special accelerators designed specifically for deep learning. TPUs provide more energy efficiency than GPUs and are optimized for tasks such as matrix multiplication, which are common in deep learning models. TPUs typically offer better performance-per-watt resolution but can have limitations that limit simplicity compared to GPUs. FPGAs (Field Programmable Gate Arrays) offer highly scalable systems, which can be tailored to specific deep learning applications. While they may not match the throughput of GPUs or TPUs in all cases, their reconfigurability makes them more efficient in power consumption and latency for application specific ASICs (Application-Specific Integrated Circuits) are optimized for specific applications and good performance energy efficiency provide well-defined use cases f but their lack of flexibility and high development costs make them less suitable for applications that require frequent updating or replacement.

#### 5.3 Trade-offs between Speed, Power Consumption, and Model Performance

When using hardware accelerators, there is always a trade-off between speed (throughput and latency), power consumption, and model performance. For example, while GPUs provide high throughput, they consume more power than TPUs or FPGAs. On the other hand, TPUs provide better energy efficiency, but may not be as flexible as a GPU for non-standard deep learning models. Similarly, FPGAs can be customized for specific applications to reduce power consumption, but their configuration process is complex and time-consuming. ASICs, while offering excellent power and performance, come at a high development cost and lack mass processing capabilities. Choosing the right hardware accelerators depends largely on specific application needs, including whether the priority is real-time performance, long battery life, or model compatibility Useful information review As hardware accelerators work in real-world situations It provides valuable insight into what it is doing. The two main applications where deep learning is commonly used on edge devices are computer vision and natural language processing (NLP). Models such as YOLO are commonly used in computer vision tasks, such as object recognition or image segmentation. For example, using YOLO on a wearable device like the NVIDIA Jetson Nano means a balance between real-time performance (low latency) and power consumption. In this case, the Jetson Nano GPU can handle object recognition with higher efficiency, making it suitable for applications such as surveillance or autonomous vehicles. In NLP applications, transformer-based models such as BERT can be applied to edge devices to enable real-time speech understanding or text classification. The use of hardware accelerators such as TPUs or FPGAs is crucial to maintain low latency and ensure that these devices can process speech data efficiently, even discreetly in low-power environments e.g mobile devices or wearable technology in real-world edge situations. With cameras, IoT devices and health monitoring systems, minimal energy consumption and consistent operations are essential. For example, deploying AI models to edge devices in industrial IoT environments requires accelerators that can handle continuous data input while reducing power consumption and maintaining reliability This information shows the impact of hardware accelerators in practical real-world applications which is how the trade-offs between speed, power and accuracy can be balanced to meet the specific requirements of each use-case.

#### 6. CONCLUSION

Efficient hardware speed is essential to balance the performance, power consumption, and real-time processing requirements of deep learning on edge devices Several techniques, such as model compression, can enhance computational efficiency a there is an increase in deep learning models on the hardware of critical objects. including pruning, quantization, and knowledge distillation), optimization of memory management, and parallelization strategies, have proven effective These techniques help reduce the size of models and reduce critical computational power without significantly compromising accuracy .Furthermore, using specialized hardware accelerators such as GPUs, TPUs, FPGAs, and ASICs enables deep learning models to run efficiently on edge devices. Each hardware type offers unique benefits and trade-offs. GPUs provide good throughput but consume power, TPUs provide power efficiency for conventional deep learning, FPGAs are customizable and power efficient, ASICs provide high performance and energy savings for migrated tasks committed but inflexible Best practices for implementing deep learning on edge devices It occurs -Whether it prioritizes speed, energy efficiency, resource abundance and model compression and optimization techniques used to reduce computing load Furthermore, choosing the right balance between throughput, latency, power consumption, and accuracy is essential to ensure that edge AI solutions meet technical and practical requirements on. The findings have important implications for industry and research, especially as edge AI becomes increasingly popular in areas such as autonomous driving, smart cities,

healthcare, and roadside technologies which acts upon itself. Optimizing hardware and software for developers is essential to ensure that AI applications deployed in the stream can perform well under severe resource constraints as more IoT devices and edge computing systems come online, adopt hardware accelerators to suit industries' specific use cases will need and ensure that their software, including machine-learning models, is optimized for the chosen hardware Energy-efficient hardware accelerators and model optimization approaches will be pursued has been for the research is a promising area. The fast pace of AI work requires new algorithms that can handle increasingly complex instances while managing capacity and latency constraints Additionally, improving model compression techniques and finding new ways to seamlessly embed deep learning into edge hardware will be critical to pushing the limits of what can be done with edge AI beyond the need to standardize the benchmarking tools and methods It cannot be . As more edge devices and models are developed, creating benchmarks that test performance and energy efficiency across different hardware platforms will help ensure that deep learning models are used effectively in different environments Looking ahead Long term perspective have many future developments in deep learning and their rise. A key trend is the increasing integration of neuromorphic computing and bioinspired architectures, aiming to mimic the functioning of the human brain. These systems have the ability to deliver extremely low voltage, highly parallel, which is ideal for edge applications. Furthermore, AI in the quantum computing stream can transform workloads, leading to more powerful models that can be run on fewer computing resources Another important aspect is the widespread use of integrated learning, which can train AI models on multiple stream machines without sending data to a centralized central server. This decentralized approach not only enhances privacy and security but reduces bandwidth and cloud resource power requirements, making edge AI ideal for applications where connectivity may be limited or data sensitivity may be a concern Eventually as edge AI continues to gain cross-compatibility frameworks It will be important for such frameworks that allow seamless integration between hardware accelerators and AI models to help standardize deployment and optimization processes across platforms, and for faster development cycles and better utilization of edge devices.

#### **Funding:**

This study did not receive any form of external financial assistance or grants. The authors confirm that all research costs were covered independently.

#### **Conflicts of Interest:**

The authors have no conflicts of interest to disclose.

#### **Acknowledgment:**

The authors are sincerely grateful to their institutions for their continued support and trust, which greatly contributed to the completion of this research.

#### References

- M. M. H. Shuvo, S. K. Islam, J. Cheng, and B. I. Morshed, "Efficient acceleration of deep learning inference on resource-constrained edge devices: A review," Proc. IEEE, vol. 111, no. 1, pp. 42–91, 2022.

P. Dhilleswararao, S. Boppu, M. S. Manikandan, and L. R. Cenkeramaddi, "Efficient hardware architectures for accelerating deep neural networks: Survey," IEEE Access, vol. 10, pp. 131788–131828, 2022.

J. Lee and H. J. Yoo, "An overview of energy-efficient hardware accelerators for on-device deep-neural-network training," IEEE Open J. Solid-State Circuits Soc., vol. 1, pp. 115–128, 2021.

G. Verma, Y. Gupta, A. M. Malik, and B. Chapman, "Performance evaluation of deep learning compilers for edge inference," in 2021 IEEE Int. Parallel Distrib. Process. Symp. Workshops (IPDPSW), 2021, pp. 858–865.

D. Ghimire, D. Kil, and S. H. Kim, "A survey on efficient convolutional neural networks and hardware acceleration."

- Interence, in 2021 IEEE Int. Parallel Distrib. Process. Symp. Workshops (IPDPSW), 2021, pp. 858-865.

[5] D. Ghimire, D. Kil, and S. H. Kim, "A survey on efficient convolutional neural networks and hardware acceleration," Electronics, vol. 11, no. 6, p. 945, 2022.

[6] C. Latotzke and T. Gemmeke, "Efficiency versus accuracy: A review of design techniques for DNN hardware accelerators," IEEE Access, vol. 9, pp. 9785-9799, 2021.

[7] Q. Zhou et al., "On-device learning systems for edge intelligence: A software and hardware synergy perspective," IEEE Internet Things J., vol. 8, no. 15, pp. 11916-11934, 2021.

[8] K. S. Zaman, M. B. I. Reaz, S. H. M. Ali, A. A. Bakar, and M. E. H. Chowdhury, "Custom hardware architectures for deep learning on portable devices: A review," IEEE Trans. Neural Netw. Learn. Syst., vol. 33, no. 11, pp. 6068-6088, 2021.

[9] M. Xia et al. "SparkNoC: An energy afficiency EPGA based accelerator using entimized lightweight CNN for edge.

- 6088, 2021.

[9] M. Xia et al., "SparkNoC: An energy-efficiency FPGA-based accelerator using optimized lightweight CNN for edge computing," J. Syst. Archit., vol. 115, p. 101991, 2021.

[10] D. Liu, H. Kong, X. Luo, W. Liu, and R. Subramaniam, "Bringing AI to edge: From deep learning's perspective," Neurocomputing, vol. 485, pp. 297–320, 2022.

[11] P. Kang and A. Somtham, "An evaluation of modern accelerator-based edge devices for object detection applications," Mathematics, vol. 10, no. 22, p. 4299, 2022.

[12] H. Feng, G. Mu, S. Zhong, P. Zhang, and T. Yuan, "Benchmark analysis of yolo performance on edge intelligence devices," Cryptography, vol. 6, no. 2, p. 16, 2022.

[13] G. Armeniakos, G. Zervakis, D. Soudris, and J. Henkel, "Hardware approximate techniques for deep neural network accelerators: A survey," ACM Comput. Surv., vol. 55, no. 4, pp. 1–36, 2022.

[14] H. Wang et al., "A comprehensive survey on training acceleration for large machine learning models in IoT," IEEE Internet Things J., vol. 9, no. 2, pp. 939–963, 2021.

- Internet Things J., vol. 9, no. 2, pp. 939–963, 2021.

[15] Q. Zhang et al., "A comprehensive benchmark of deep learning libraries on mobile devices," in Proc. ACM Web Conf. 2022, 2022, pp. 3298–3307.

- [16] D. Zhang et al., "A full-stack search technique for domain optimized deep learning accelerators," in Proc. 27th ACM Int. Conf. Archit. Support Program. Lang. Oper. Syst., 2022, pp. 27–42.

[17] T. Zhao et al., "A survey of deep learning on mobile devices: Applications, optimizations, challenges, and research opportunities," Proc. IEEE, vol. 110, no. 3, pp. 334–354, 2022.

[18] H. Wang et al., "Enabling micro AI for securing edge devices at hardware level," IEEE J. Emerg. Sel. Top. Circuits Syst., vol. 11, no. 4, pp. 803–815, 2021.

[19] H. Cai et al., "Enable deep learning on mobile devices: Methods, systems, and applications," ACM Trans. Des. Autom. Electron. Syst. vol. 27, no. 3, pp. 1–50, 2022.

- Electron. Syst., vol. 27, no. 3, pp. 1–50, 2022. [20] B. Varghese et al., "A survey on edge performance benchmarking," ACM Comput. Surv., vol. 54, no. 3, pp. 1–33,

- 2021

- [21] M. S. Murshed et al., "Machine learning at the network edge: A survey," ACM Comput. Surv., vol. 54, no. 8, pp. 1–37, 2021.

[22] S. Zhu, K. Ota, and M. Dong, "Energy-efficient artificial intelligence of things with intelligent edge," IEEE Internet Things J., vol. 9, no. 10, pp. 7525–7532, 2022.

[22] V. Lingted, "Collaboration of the same with EDCA based CDIM conclusion for energy efficient and time same with EDCA.

- [23] X. Liu et al., "Collaborative edge computing with FPGA-based CNN accelerators for energy-efficient and time-aware face tracking system," IEEE Trans. Comput. Social Syst., vol. 9, no. 1, pp. 252–266, 2021.

[24] H. Zhou et al., "Accelerating deep learning inference via model parallelism and partial computation offloading," IEEE Trans. Parallel Distrib. Syst., vol. 34, no. 2, pp. 475–488, 2022.

[25] I. Damaj et al., "Intelligent transportation systems: A survey on modern hardware devices for the era of machine learning," J. King Saud Univ.-Comput. Inf. Sci., vol. 34, no. 8, pp. 5921–5942, 2022.